版權說明:本文檔由用戶提供并上傳,收益歸屬內容提供方,若內容存在侵權,請進行舉報或認領

文檔簡介

1、西安電子科技大學西安電子科技大學 XIDIDIAN UNIVERSITYXIDIDIAN UNIVERSITY第四章第四章 MOSMOS場效應晶體管場效應晶體管MOSFETMOSFET頻率特性和頻率特性和CMOSCMOS開關開關2022-6-241場效應器件物理場效應器件物理4.2 MOSFET 本節內容本節內容p MOSFET等效電路等效電路p 頻率限制因素頻率限制因素p NMOS開關開關p CMOS電路電路2022-6-242022-6-2434.2 MOSFET 等效電路等效電路概述概述p等效電路是器件模型的一種形式,用于器件的仿真等效電路是器件模型的一種形式,用于器件的仿真p仿真:仿真

2、:利用電路仿真軟件利用電路仿真軟件圍繞圍繞器件建立電路的器件建立電路的IV關系關系,對電路進行對電路進行仿真仿真驗證,驗證,仿真仿真是是一數學求解的過程一數學求解的過程u仿真時,無真正仿真時,無真正的的器件,元器件器件,元器件要用模型和模型參數來要用模型和模型參數來替代替代p模型:反映器件特性,可采用數學表達式、等效電路等形式模型:反映器件特性,可采用數學表達式、等效電路等形式u常用模型:等效電路常用模型:等效電路模型模型u模型參數:描述等效電路中各元件值所用的參數模型參數:描述等效電路中各元件值所用的參數。2022-6-2444.2 MOSFET MOSFETMOSFET等效電路:等效元器件

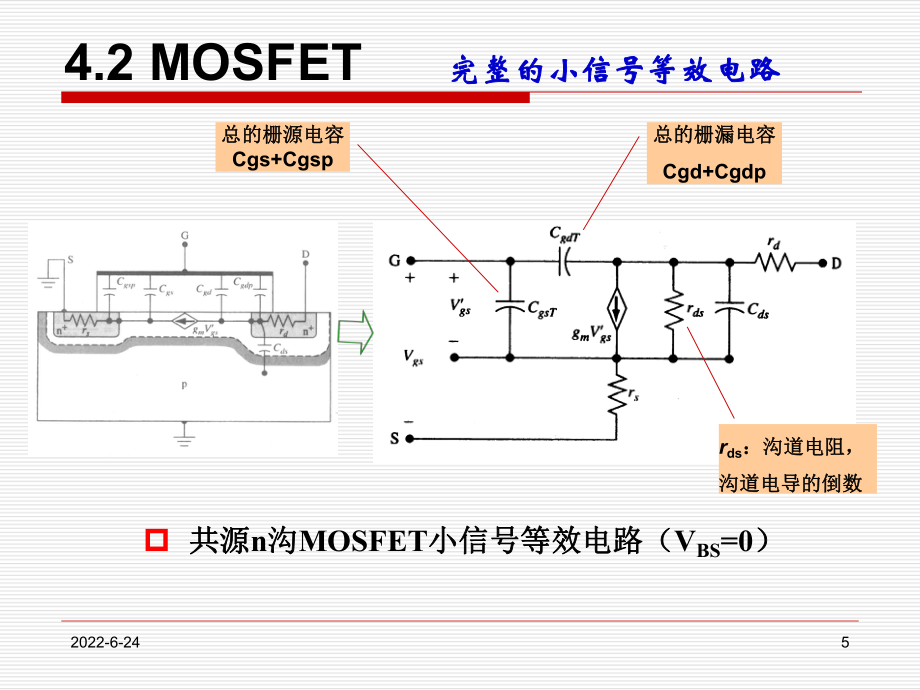

3、等效電路:等效元器件源極串聯電阻源極串聯電阻柵源交疊電容柵源交疊電容漏極串聯電阻漏極串聯電阻柵漏交疊電容柵漏交疊電容漏漏-襯底襯底pn結電容結電容柵源電容柵源電容柵漏電容柵漏電容跨導跨導寄生參數寄生參數本征參數本征參數pG-S:Cgs,Cgsp,rs;pG-D:Cgd,Cgdp ,rd;uCgs,Cgd: 體現了柵和源、漏體現了柵和源、漏附近的附近的溝道電荷間的相互作用溝道電荷間的相互作用線性區:線性區: Cgs Cgd (CoxWL)/2飽和區:飽和區: Cgd 0, Cgs2 (CoxWL)/3uCgsp,Cgdp:交疊電容交疊電容pD-S:gm , Id gmVgsCds:漏:漏-襯底襯

4、底pn結電容結電容 (DB結勢壘電容結勢壘電容BS結勢壘電容)結勢壘電容)2022-6-2454.2 MOSFET 完整的小信號等效電路完整的小信號等效電路p 共源共源n溝溝MOSFET小信號等效電路(小信號等效電路(VBS=0)總的柵源電容總的柵源電容Cgs+Cgsp總的柵漏電容總的柵漏電容Cgd+Cgdprds:溝道電阻,:溝道電阻,溝道電導的倒數溝道電導的倒數4.2 MOSFET 模型參數模型參數p模型參數:描述等效電路中各元件值所用的參數。模型參數:描述等效電路中各元件值所用的參數。p與與IDS相關的模型參數:相關的模型參數:W,L,KP(ucox),LAMBDAp與與VT相關的模型參

5、數:相關的模型參數:VT0,GAMMA, PHIp與柵相關的三個電容參數:與柵相關的三個電容參數:CGD,CGS,CGB2022-6-246)(DSTGSoxnsatDVVVLCWI1)(22)()(222DSDSTGSoxnDVVVVLCWI體效應系數)()(:22q222q222q2SS0fpfpafpafpaSBTSBoxmsfpoxssoxmsfpoxssoxSBTNVVVCNCQCNCQCVNV4.2 MOSFET 模型和模型參數特點模型和模型參數特點o隨著溝長的縮短,短溝窄溝效應凸現,隨著溝長的縮短,短溝窄溝效應凸現,IV公式和閾值電壓公式都需修公式和閾值電壓公式都需修正,模型的發

6、展級別特別多,模型也越來越復雜。正,模型的發展級別特別多,模型也越來越復雜。Berkly Short-channel IGET Model 2022-6-2472022-6-2484.2 MOSFET MOSFETMOSFET頻率限制頻率限制pMOSFET可作為放大器件,工作頻率能不能無限大?可作為放大器件,工作頻率能不能無限大?uMOSFET存在很多電容,包括本征電容和寄生電容存在很多電容,包括本征電容和寄生電容u輸入工作頻率不同,器件電容的容抗不同輸入工作頻率不同,器件電容的容抗不同u頻率太高,器件輸出可能無法響應輸入的變化,器件的特性變頻率太高,器件輸出可能無法響應輸入的變化,器件的特性

7、變差,甚至無法實現放大。差,甚至無法實現放大。2022-6-2494.2 MOSFET MOSFETMOSFET頻率限制因素頻率限制因素p限制因素限制因素2:柵電容充放電需要的時間:柵電容充放電需要的時間u截止頻率截止頻率fT:器件電流增益為:器件電流增益為1時的時的頻率頻率p限制因素限制因素1:溝道載流子的溝道渡越時間溝道載流子的溝道渡越時間m1設溝道長度cm/s710飽和漂移速度MOSFET Si對LslvGHz1001ps10ttsltfvL截止頻率溝道渡越時間溝道渡越時間通常不是溝道渡越時間通常不是主要頻率限制因素主要頻率限制因素1TidIIff2022-6-24104.2 MOSFE

8、T 電流電流- -頻率關系頻率關系負載電阻負載電阻)(dVgsVTgdCjgsVTgsCjiIgsMTgsgsLmTgdTgsgsTgdLLmTgdTgsiVCCjVRgCCjVCRjRgCCjI)1 (11輸入電流輸入電流輸出電流輸出電流u密勒效應:密勒效應:將跨越輸入將跨越輸入-輸出端的電容等效到輸入端,輸出端的電容等效到輸入端,C值會擴大(值會擴大(1K)倍,)倍,K為常數為常數)(/gsVdVTgdCjgsVmgLRdVdI)1 (LmTgdMRgCC密勒電容1TgdLCR通常u共源連接的共源連接的NMOS:輸入端:輸入端GS,輸入電流,輸入電流Ii,即柵壓對,即柵壓對MOS電容電容的

9、充放電電流;輸出端的充放電電流;輸出端DS,輸出電流,輸出電流Id2022-6-24114.2 MOSFET 含有密勒電容等效電路含有密勒電容等效電路)1 (LmTgdMRgCC密勒電容p輸入電流公式:輸入電流公式:p米勒電容對米勒電容對MOSFET輸入阻抗的影響:輸入阻抗的影響:u使輸入阻抗減小使輸入阻抗減小gsMTgsgsLmTgdTgsgsTgdLLmTgdTgsiVCCjVRgCCjVCRjRgCCjI)1 (112022-6-24124.2 MOSFET 截止頻率推導截止頻率推導)(2MTgsmidgsmdgsMTgsiCCfgIIVgIVCCjI電流增益輸出電流輸入電流MCTgsC

10、GCmgGCmgMCTgsCmgIIffid等效輸入柵極電容跨導截止頻率2)(21T的倒數溝道長度的平方遷移率在理想情況下,飽和區22G2)()(, 0LLVVfVVLCWgWLCCCCnTGSnTTGSoxnmoxgsTgdT2022-6-24134.2 MOSFET 提高頻率特性途徑提高頻率特性途徑p提高遷移率(提高遷移率(100方向,工藝優質)方向,工藝優質)p縮短縮短Lp減小寄生電容減小寄生電容的倒數溝道長度的平方遷移率在理想情況下,222)(LLVVfnTGSnT)(22TTMTgsmTgsmCCgfCgf,實際理想截止頻率)1 (LmTgdMRgCC密勒電容,pspssgdgdTg

11、dggTgCCCCCC2022-6-24144.2 MOSFET 開關原理開關原理p共源連接的共源連接的MOS開關相當于一個反相器開關相當于一個反相器uVIN=VDD,NMOS導通,穩態時導通,穩態時MOSFET處于深線性處于深線性RonRL,VOUT=VDD;p反相器電路反相器電路uNMOS工藝:耗盡型工藝:耗盡型NMOS作為負載,直流功耗大作為負載,直流功耗大uCMOS工藝:增強型工藝:增強型PMOS作為負載,即作為負載,即CMOS反相器(均為增強性器件)反相器(均為增強性器件)4.2 MOSFET CMOS導向器導向器pCMOS(Complentary 互補互補CMOS)u n溝溝MOS

12、FET與與p溝溝MOSFET互補互補u 實現低功耗、全電平擺幅實現低功耗、全電平擺幅u 數字邏輯電路的首選工藝數字邏輯電路的首選工藝p阱:局部襯底阱:局部襯底P阱阱4.2 MOSFET CMOS導向器導向器pNMOS高導通高導通(VIN=VDD ),PMOS低導通低導通(VIN=0)uVIN=VDD,VGSN=VDDVTN,NMOS導通導通uVIN=0,VGSP=-VDDVTP,PMOS導通導通4.2 MOSFET CMOSpt1t1時刻,時刻,VoutVout初初=0=0。ViVi1 1到到0, PMOS0, PMOS導通,導通,V VSDSD始始= =VDDVDD,有,有I ID D對對C

13、 CL L充電,隨著充電充電,隨著充電的進行,的進行,V VOutOut上升,上升,V VSDSD下降,脫離飽和區后,下降,脫離飽和區后,I ID D減小,直到減小,直到V VSDSD0 0,I ID D0 0 ,V VOutOutV VOHOH=VDD=VDD,充電完成。隨后,充電完成。隨后,VinVin維持低,靜態維持低,靜態,I,ID D0 0。pt2t2時刻,時刻, ViVi0 0到到1, nMOS1, nMOS導通,導通,V VDSDS始始= =VDDVDD,有,有I ID D,C CL L通過通過NMOSNMOS放電,隨著放電的放電,隨著放電的進行,進行,V Voutout下降,下

14、降,V VDSDS下降,脫離飽和區后,下降,脫離飽和區后,I ID D減小,直到減小,直到V VSDSD0 0,I ID D0 0 ,V VOutOutV VOLOL=0=0,放電完成。隨后,放電完成。隨后,VinVin維持高,靜態維持高,靜態,I,ID D0 0。pCMOS如何實現低功耗,全電平擺幅?如何實現低功耗,全電平擺幅?nCLT:輸出端對地總電容:輸出端對地總電容(下一級負載下一級負載C、引線、引線C、 NMOS和和PMOS的漏襯的漏襯PN結結C)4.2 MOSFET CMOS反相器反相器2022-6-2418p全電平擺幅:全電平擺幅:VOH- VOL=VDD-0=VDDp靜態功耗:

15、充放電完成后電路的功耗,近似為零,靜態功耗:充放電完成后電路的功耗,近似為零, 靜態時一管導通,另一管截止,不存在直流通路靜態時一管導通,另一管截止,不存在直流通路p動態功耗:輸入高低電平轉換過程中的功耗。動態功耗:輸入高低電平轉換過程中的功耗。u對對CLT充放電的功耗充放電的功耗 + N、P兩管同時導兩管同時導通時的功耗通時的功耗u減小寄生電容,減小減小寄生電容,減小高低電平高低電平轉換的時間轉換的時間p開關時間:輸出相對于輸入的時間延遲,包括導通時間開關時間:輸出相對于輸入的時間延遲,包括導通時間t tonon和關斷時間和關斷時間t toffoffu載流子溝道輸運時間,(本征延遲)載流子溝道輸運時間,(本征延遲)u輸出端對地電容的充放電時間。(負載延遲)輸出端對地電容的充放電時間。(負載延遲)p提高開關速度途徑(降低開關時間):提高開關速度途徑(降低開關時間):u減小溝長減小溝長L L(L5um,L5um,開關速度由負載延遲決定)開關速度由負載延遲決定)u減小對地總電容:引線電容、減小對地總電容:引線電容、NOMS PMOSNOMS PMOS的的DBDB間間PNPN結電容等寄生電容結電容等寄生電容u增加跨導,提高充放電電流。(跨導和增加跨導,提高充放電電流。(跨導和I I都正比于增益因子)都正比于增益因子)2022-6-24194.2 MOSFET 開關時間開關時間20

溫馨提示

- 1. 本站所有資源如無特殊說明,都需要本地電腦安裝OFFICE2007和PDF閱讀器。圖紙軟件為CAD,CAXA,PROE,UG,SolidWorks等.壓縮文件請下載最新的WinRAR軟件解壓。

- 2. 本站的文檔不包含任何第三方提供的附件圖紙等,如果需要附件,請聯系上傳者。文件的所有權益歸上傳用戶所有。

- 3. 本站RAR壓縮包中若帶圖紙,網頁內容里面會有圖紙預覽,若沒有圖紙預覽就沒有圖紙。

- 4. 未經權益所有人同意不得將文件中的內容挪作商業或盈利用途。

- 5. 人人文庫網僅提供信息存儲空間,僅對用戶上傳內容的表現方式做保護處理,對用戶上傳分享的文檔內容本身不做任何修改或編輯,并不能對任何下載內容負責。

- 6. 下載文件中如有侵權或不適當內容,請與我們聯系,我們立即糾正。

- 7. 本站不保證下載資源的準確性、安全性和完整性, 同時也不承擔用戶因使用這些下載資源對自己和他人造成任何形式的傷害或損失。

最新文檔

- 鄉鎮街加班管理制度

- 公司全套印章管理制度

- 韓式烤肉后廚管理制度

- 高效完成工作管理制度

- 餐飲設備維護管理制度

- 西固少兒書法管理制度

- 車輛安全管理管理制度

- 車站設備安全管理制度

- 領導特殊食堂管理制度

- 餐飲連鎖工裝管理制度

- 總監答辯題庫

- 醫務科醫療質量管理工作計劃

- 四年級英語教學計劃及質量提升方案

- 新視野大學英語(第四版)讀寫教程3(思政智慧版)課件 B3U5 Chinas space dream Section A

- 2023-2024學年廣東省深圳市寶安區富源學校七年級(下)期中數學試卷(含答案)

- 瓶瓶罐罐做花瓶課件

- 創意設計工作室合伙合同

- 浙江省杭州市學軍小學數學六年級小升初期末復習試卷(含答案)

- 【年加工500噸鮑魚的綜合加工生產工藝設計10000字(論文)】

- JBT 7387-2014 工業過程控制系統用電動控制閥

- 湖南省長沙市瀏陽市2023-2024學年七年級下學期期中數學試題(含解析)

評論

0/150

提交評論