版權說明:本文檔由用戶提供并上傳,收益歸屬內容提供方,若內容存在侵權,請進行舉報或認領

文檔簡介

1、.摘要采用自上向下的設計方法,設計了基于復雜可編程邏輯器件的數字頻率計。以AT89C51單片機作為系統的主控部件,完成電路的測試信號控制、數據運算處理、鍵盤掃描和控制數碼管顯示。用VHDL語言編程,由CPLD(plex Programmable Logic Device)完成各種時序控制及計數功能。該系統具有結構緊湊、可靠性高、測頻X圍寬和精度高等特點。關鍵詞 可編程邏輯器件 CPLD 等精度測量法 單片機 VHDLAbstactWith the adoption of the top-down design method and AT89C51 SCMC (Single Chip Mico

2、puter) as the master control ponent of the system,the circuit test signalcontrolling,data operation processing,keyboard scanning,and nixie tube display as well were pleted by the digital cymometer.A CPLD programmed by VHDL,realized various sequence control and count functions.The system is character

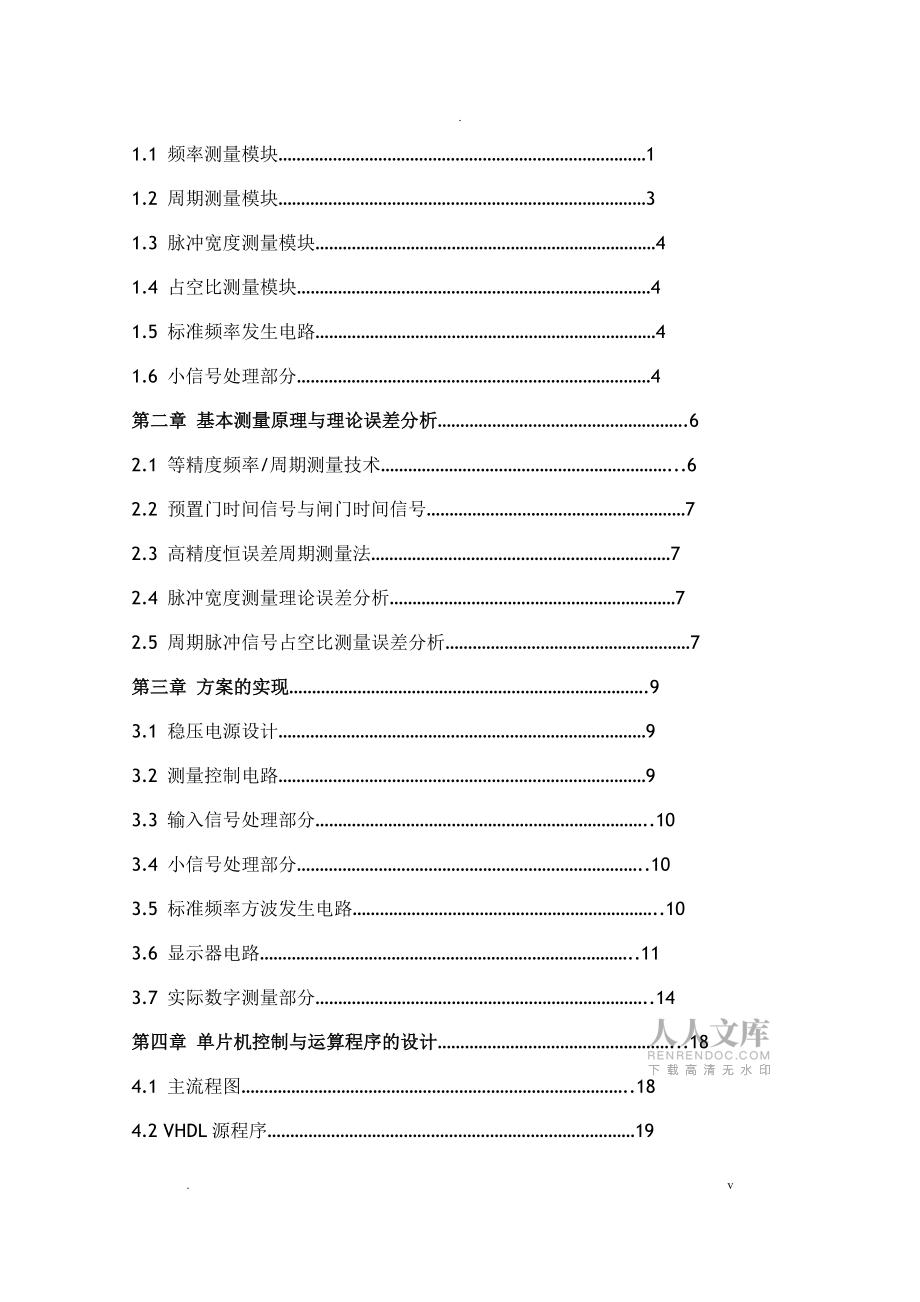

3、ized by impact structure,high reliability,high precision,and wide frequency-test-range. Key Words:programmable logic ponent CPLD measures mensurationsingle chip mico puter VHDL目錄摘要.英文摘要.緒論.第一章 設計方案選擇.11.1 頻率測量模塊11.2 周期測量模塊31.3 脈沖寬度測量模塊41.4 占空比測量模塊41.5 標準頻率發生電路41.6 小信號處理部分4第二章 基本測量原理與理論誤差分析.62.1 等精度頻

4、率/周期測量技術.62.2 預置門時間信號與閘門時間信號72.3 高精度恒誤差周期測量法72.4 脈沖寬度測量理論誤差分析72.5 周期脈沖信號占空比測量誤差分析7第三章 方案的實現.93.1 穩壓電源設計93.2 測量控制電路93.3 輸入信號處理部分.103.4 小信號處理部分.103.5 標準頻率方波發生電路.103.6 顯示器電路.113.7 實際數字測量部分.14第四章 單片機控制與運算程序的設計.184.1 主流程圖.184.2 VHDL源程序19第五章 結束語.25致謝.26參考文獻.27緒論數字頻率計是數字電路中的一個典型應用,是計算機、通訊設備、音頻視頻等科研生產領域不可缺少

5、的測量儀器。實際的硬件設計用到的器件較多,連線比較復雜,而且會產生比較大的延時,造成測量誤差、可靠性差。隨著復雜可編程邏輯器件(CPLD)的廣泛應用,以EDA工具作為開發手段,運用VHDL語言,將使整個系統大大簡化, 提高整體的性能和可靠性。采用VDHL編程設計實現的數字頻率計,除被測信號的整形部分、鍵輸入部分和數碼顯示部分以外,其余全部在一片FPGA芯片上實現,整個系統非常精簡,而且具有靈活的現場可更改性。在不更改硬件電路的基礎上,對系統進行各種改進還可以進一步提高系統的性能。該數字頻率計具有高速、精確、可靠、抗干擾性強和現場可編程等優點。本文用VHDL在CPLD器件上實現一種8b數字頻率計

6、測頻系統,能夠用十進制數碼顯示被測信號的頻率,不僅能夠測量正弦波、方波和三角波等信號的頻率,而且還能對其他多種物理量進行測量。具有體積小、可靠性高、功耗低的特點。CPLD是一種新興的高密度大規模可編程邏輯器件,它具有門陣列的高密度和PLD器件的靈活性和易用性,目前已成為一類主要的可編程器件。可編程器件的最大特點是可通過軟件編程對其器件的結構和工作方式進行重構,能隨時進行設計調整而滿足產品升級。使得硬件的設計可以如軟件設計一樣方便快捷,從而改變了傳統數字系統及用單片機構成的數字系統的設計方法、設計過程及設計概念,使電子設計的技術操作和系統構成在整體上發生了質的飛躍。采用CPLD可編程器件,可利用

7、計算機軟件的方式對目標期進行設計,而以硬件的形式實現。既定的系統功能,在設計過程中,可根據需要隨時改變器件的內部邏輯功能和管腳的信號方式,借助于大規模集成的CPLD和高效的設計軟件,用戶不僅可通過直接對芯片結構的設計實現多種數字邏輯系統功能,而且由于管腳定義的靈活性,大大減輕了電路圖設計和電路板設計的工作量及難度,同時,這種基于可編程芯片的數量,縮小了系統的體積,提高了系統的可靠性。EDA(電子設計自動化)技術就是以計算機為工具,在EDA軟件平臺上,對硬件語言HDL為系統邏輯描述手段完成的設計文件,自動的完成邏輯編譯、邏輯化簡、邏輯綜合及優化、邏輯仿真,直至對特定目標芯片的適配編譯、邏輯映射和

8、編程下載等工作(文本選用的開發工具為Altera公司的MAX+PLUSII)。EDA的仿真測試技術只需要通過計算機就能對所設計的電子系統從各種不同層次的系統性能特點完成一系列準確的測試與仿真操作,大大提高了大規模系統電子設計的自動化程度。設計者的工作僅限于利用軟件方式,即利用硬件描述語言(如VHDL)來完成對系統硬件功能的描述。 VHDL(VeryHigh Speed Integrated Circuit HardwareDetionLanguage,超高速集成電路硬件描述語言)誕生于1982年,是由美國國防部開發的一種快速設計電路的工具,目前已經成為IEEE(TheInstituteof E

9、lectricalandElectronicsEngineers)的一種工業標準硬件描述語言。相比傳統的電路系統的設計方法,VHDL具有多層次描述系統硬件功能的能力,支持自頂向下(ToptoDown)和基于庫(LibraryBased)的設計的特點,因此設計者可以不必了解硬件結構。從系統設計入手,在頂層進行系統方框圖的劃分和結構設計,在方框圖一級用VHDL對電路的行為進行描述,并進行仿真和糾錯,然后在系統一級進行驗證,最后再用邏輯綜合優化工具生成具體的門級邏輯電路的網表,下載到具體的CPLD器件中去,從而實現可編程的專用集成電路(ASIC)的設計。第1章設計方案的選擇根據頻率計的設計要求,電路

10、系統可劃分為幾個基本模塊,如圖1.1所示: 波形整形電路 前置放大電路 頻率, 周期測量電路 標準頻率信號發生電路占空比測量 電路脈沖寬度測量電路脈沖信號處理電路 穩壓電源 顯示電路 控制與數據 處理電路被測信號輸入預置門控信號圖1.1 頻率計組成模塊框圖1.1 頻率測量模塊1.1.1直接測量法大家都知道,如果根據基本原理實現對頻率的數字化測量,是一種直接測量的手段,這種方法比較簡單,如果能滿足設計要求的話,應該作為首要的選擇方案。下面我們簡單分析一下使用該方法是否能滿足設計要求,把被測頻率信號經脈沖整形電路處理后加到閘門的一個輸入端,只有在閘門開通時間T(以秒計)內,被計數的脈沖送到十進制計

11、數器進行計數。設計數器的值為N,則可以得到被測信號頻率為f = N / T,經過對照數字化直接測量頻率的原理我們可以發現,本測量在低頻率段的相對測量誤差較大,即在低頻率段不能滿足本設計的要求。1.1.1計數式測頻的原理方框圖1.1.2組合測頻法是指在高頻時采用直接測量法,低頻時采用直接測量周期法測信號的周期,然后換算成頻率。這種方法可以在一定程度上彌補方法(1)的不足,但是難以確定最佳分測點,而且電路實現比較復雜。 1.1.2直接測頻和直接測周期的量化誤差1.1.3倍頻法是指把頻率測量X圍分成多個頻率段,使用倍頻技術,根據頻率段設置倍頻系數,將經過整形的低頻信號進行倍頻后再進行測量,對高頻率段

12、則直接進行測量,倍頻法比較難以實現。1.1.4等精度測頻法通過對傳統的測量方法的分析與研究,結合高精度恒誤差測量原理,我們設計了一種測量精度與被測頻率無關的硬件測頻電路。本方法立足于快速的寬位數高精度浮點數字運算。其實現方式可以用圖1.2來說明。圖中,預置門控制信號是寬度為Tpr的一個脈沖,T1和T2是兩個可控計數器。標準頻率信號從T1的時鐘輸入端CLK輸入,其頻率為fs,經過整形后的被測信號從T2的時鐘輸入端CLK輸入,設其實際頻率為fx,當預置門信號為高電平時,經過整形后的被測信號的上升沿通過D觸發器的Q端同時啟動計數器T1和T2。T1和T2分別對被測信號和標準頻率信號同時計數。當預置門信

13、號為低電平時,隨后而至的被測信號的上升沿將使兩個計數器同時關閉。CLKENCLK T2 OUT2CLRCLKENCLK T1 OUT1CLRD Q預置門控信號標準頻率信號被測信號清零信號圖1.2 等精度測頻法原理框圖設在一次預置門時間Tpr內對被測信號的計數為Nx,對標準的計數值為Nx,則下式成立: fx / Nx = fs / Ns -(式1.1) 由此可推得 fx = fs Nx / Ns -(式1.2)相對誤差公式 = ( 2 / Ns + fs / fs ) -(式1.3)從誤差分析中可以看出來, 它的測量精度與Ns和標準頻率精確度有關, 而與被測頻率無關. 顯然, Ns決定于預置門時

14、間和標準頻率信號的頻率, 其關系式如下: Ns = Tpr fs -(式1.4)如果采用頻率為50MHz的晶體震蕩器, 則有: | 1 / Ns -(式1.5)如果預置門時間Tpr = 0.1s, 則: Ns = 0.1 60 000 000 = 6 000 000, | 1.5 10-6以上四種方法中, 倍頻法雖然在理論上可以達到很高的精度, 但是在低頻段, 就目前常規的鎖相器件而言, 鎖相電路工作性能不理想, 頻率小于100Hz時甚至不能工作.前三種方法本質上都是立足于頻率基本定義, 沒有擺脫傳統的測量方法的局限, 從下文的詳細論述中可以看出, 用方法(4)可以用單片機程序方便地完成寬位浮

15、點數的數學運算, 實現高精度測量.基于上述論證以及第二部分中詳細的理論分析, 我們準備選擇方法(4). 1.2 周期測量模塊1.2.1直接周期測量法用被測信號經過放大整形后形成的方波信號直接控制計數門控電路, 使主門開放時間等于信號周期Tx, 時標為Ts的脈沖在主門開放時間進入計數器. 設在Tx期間計數值為N, 可以根據以下公式來算得被測信號周期: Tx = NTs -(式1.6)經過誤差分析, 可以得出結論: 用該測量法測量的時候, 被測信號的頻率越高, 測量誤差越大.1.2.2等精度周期測量法該方法在測量電路和測量精度上與等精度頻率測量完全相同, 只是在進行計算時所用的公式不同, 用周期1

16、/T代換頻率f就可以了, 它的計算公式是: Tx = TsNs / Nx -(式1.7)從降低電路的復雜度以及提高精度(特別是高頻)上考慮, 本設計將要采用方法(2)測量被測信號的周期.1.3 脈沖寬度測量模塊在進行脈沖寬度的測量時, 首先經過信號處理電路進行處理, 限制只有信號的50%幅度以及其以上部分才能輸入數字測量部分. 脈沖邊沿被處理得非常陡峭, 然后送入測量計數器進行測量. 測量電路在檢測到脈沖信號的上升沿的時候打開計數器, 并且在檢測到下降沿的時候關閉計數器, 設脈沖寬度為Twx, 計算公式為: Twx = Nx / fs -(式1.8)1.4 占空比測量模塊測量一次脈沖信號的脈沖

17、寬度, 記錄下它的值為Twx1, 然后將信號反相, 再測量一次脈沖寬度并且記錄下它的值為Twx2, 通過下面的公式計算占空比:占空比 = Twx1100% / (Twx1 + Twx2) -(式1.9)1.5 標準頻率發生電路本模塊采用高頻率穩定度和高精度的可微調晶體振蕩器作為標準頻率發生器.1.6 小信號處理部分小信號處理部分受限于寬帶放大器的性能, 放大器電路需要附有高速整形電路. 有以下幾種方案:1.6.1采用分立元件使用場效應管做輸入極, 以提高輸入阻抗. 用截止頻率1 000MHz的三極管9018做放大極. 由于電路復雜, 需要調節的部分較多, 而且一致性差, 所以不予采用.1.6.

18、2采用運算放大器電路簡潔, 但是因為與TTL電平接口而另外需要電平移位電路. 并且需要使用運算放大器做一高速寬帶放大器, 市場上難以買到高速運算放大器, 其應用因此受到限制.1.6.3直接采用比較器采用比較器可以簡單的完成設計. 采用高速比較器LM361可以處理高達10MHz的輸入信號. LM361有低輸入失調電壓和電壓X圍靈活等特點, 響應時間最大僅20ns, 輸出電平可與TTL電平相匹配.綜合考慮, 本部分電路采用方案(3). 比較器輸入容易受到干擾, 因此電路上采用凈化電源并且需要合理安排地線. 經過最后的實際測量, 輸入靈敏度4mV左右, 完全滿足小信號測量的需要.第2章基本測量原理與

19、理論誤差分析2.1 等精度頻率/周期測量技術2.1.1量化誤差若所測頻率值為fx, 被測頻率的真實值為fxe, 標準頻率為fs, 在一次測量中, 預置門時間為Tpr, 被測信號技數值為Nx, 標準頻率信號計數值為Nx. 由于fx計數的起停時間都是由該信號的上升沿觸發的, 因此在Tpr時間內對fx的計數Nx無誤差, 在此時間內的計數Ns最多相差一個脈沖, 即et 1, 則下式成立: fx / Nx = fs / Ns -(式2.1) fxe / Nx = fs / ( Ns + et ) -(式2.2)可以分別推得 fx = fs Nx / Ns -(式2.3) fxe = fs Nx / (

20、Ns + et ) -(式2.4)根據相對誤差公式有 | = fxe / fxe = ( fxe - fx ) / fxe -(式2.5)經過整理可以得到 fxe / fxe = et / Ns -(式2.6)因為et 1, 故et / Ns 1 / Ns, 即 et / Ns 1 / NsNs = Tpr fs -(式2.7)根據以上分析, 可以知道等精度測頻法具有三個特點: 相對測量誤差與被測頻率的高低無關; 增大Tpr或fs可以增大Ns, 減少測量誤差, 提高測量精度; 測量精度與預置門寬度和標準頻率有關, 與被測信號的頻率無關, 在預置門和常規測頻閘門時間相同而被測信號頻率不同的情況下

21、, 等精度測量法的測量精度不變.2.1.2標準頻率誤差標準頻率誤差為fs / fs, 因為晶體的穩定度很高, 標準頻率誤差可以進行校準, 相對于量化誤差, 校準后的標準頻率誤差可以忽略。2.2 預置門時間信號與閘門時間信號預置門的概念與傳統的閘門的概念是不同的. 預置門是指同時啟動或同時停止標準頻率信號計數器和被測信號計數器的門控信號. 預置門的概念用于高精度恒定誤差測頻/周期方法中, 并且稱預置門的時間寬度為預置門時間.高精度恒定誤差測頻方法測量精度與預置門時間和標準頻率有關, 與被測信號的頻率無關. 在預置門時間和閘門時間相同而被測信號頻率不同的情況下, 高精度恒定誤差頻率測量法的測量精度

22、不變, 而直接測頻法的精度隨著被測信號的增加而接近線性的增大.2.3 高精度恒誤差周期測量方法分析思路和結果均對高精度恒誤差頻率測量相似或相同.2.4 脈沖寬度測量理論誤差分析根據方案中的脈沖寬度測量方法, 分析脈沖寬度測量誤差.設被測信號的脈沖寬度為Twxe, 標準頻率信號頻率為fs, 則脈沖寬度的測量值為: Twx = Nx / fs -(式2.8)在一次測量中, 對標準頻率信號的計數值Nx可能產生1個標準頻率信號周期的計數誤差, 則脈沖寬度測量相對誤差為: |Twx / Twx| = ( 1 fs ) / ( Nx fs ) = 1 / Nx -(式2.9)其中Nx = Twx fs.

23、可以看出, 在fs一定的時候, 脈沖寬度越小, 誤差越大.當Twx = 100s, fs = 60MHz時, Nx = 6 000, 則有: |Twx / Twx| = 1 / 6 000 = 0.017%2.5 周期脈沖信號占空比測量誤差分析使用第一部分中所述的占空比方法, 根據誤差合成原理, 周期測量相對誤差最大值等于脈沖寬度測量相對誤差.在標準頻率為60MHz, 被測頻率1kHz(即周期為0.001s)的時候, 設其占空比為10%, 則由脈沖寬度測量相對誤差公式計算出的相對誤差應該小于 1 / ( 0.001 10% 60 106 ) = 1 / 6000 = 0.017%第3章方案的實

24、現3.1 穩壓電源設計本項設計要求的電源有: +12V, -12V, +5V的穩壓電源. 在進行電源設計時, 功率交流輸入端加一級電源濾波器, 以降低工頻頻率干擾.3.2 測量控制電路本電路采用單片機和CPLD/FPGA的結合來實現. 單片機(AT89C51)完成整個測量電路的控制, 數據處理和顯示輸出, CPLD/FPGA完成計數器的功能. 鍵盤信號由AT89C51單片機進行處理. AT89C51從CPLD/FPGA讀回計數數據并進行高精度浮點運算, 并且向顯示電路輸出測量結果. 電路系統原理框圖如圖3.1所示: 電源 晶振信號放大與整形 電路數碼顯示LED8 顯示驅動74LS1648 P0

25、P3.0P3.1 P2 RSETP1.0P1.3 P1.0P1.3 TCLK CPLD/FPGA BCLK 占脈周頻復圖3.1 等精度數字頻率計電路系統原理框圖3.3 輸入信號處理部分為測量小信號,需要在輸入端加前置信號處理電路,將小信號放大后送入整形電路。3.4 小信號處理部分電路如圖3.2:圖3.2 小信號處理部分電路在調試中發現LM361的輸出在零瞬間有毛刺, 在輸出與地間并聯一個100pF的瓷片電容后消除了毛刺, 而且處理后的波形仍然比較陡峭, 本部分電路的抗干擾能力也很強.3.5 標準頻率方波發生電路本設計采用60MHz的晶體震蕩器產生標準頻率方波信號(頻標)供數字測量電路使用。晶體

26、震蕩器采用恒溫晶體震蕩器,穩定度為: 2.010-7 / 24小時。晶體震蕩器主要由晶體震蕩電路和緩沖放大電路組成。如下圖所示:圖3.3 60MHz的晶體震蕩電路工作原理:如圖3.3所示。晶體三極管VT1為60MHz的晶體震蕩器,震蕩器的輸出送至晶體三級管VT2的緩沖放大器進行信號放大,它的反射級有較大的反饋, 使得震蕩器更加穩定。電阻R5,R6為偏置,R7為負載電阻,信號通過電容C6耦合輸出60MHz的高頻信號。其中,VT1集電極回路由電感L1以及電容C4,C5組成并聯諧振回路,調節空氣可變電容C4,使得回路諧振在震蕩頻率60MHz上,電感L3和電容C7組成去耦電路,其作用在于濾除電源中的高

27、次諧波,以保證頻率波形的純度。3.6 顯示器電路LCD(Liquid Crystal Diodes)是液晶顯示器的簡稱。LED顯示塊是由發光二極管顯示字段的顯示器件。在本設計的系統中采用的是七段LED。這種顯示塊有陰極與共陽極兩種,如圖3.4所示。 (a)共陰極 (b)共陽極 (c)管腳配置圖3.4 七段LED顯示塊七段顯示塊與微機接口非常容易。如表3.1所示。表3.1七段LED的段選碼在微機應用系統中使用LED顯示塊構成N位LED顯示器。圖3.5是N位顯示器的構成原理。圖3.5 N位LED顯示器因為本設計用高精度恒誤差的頻率和周期測試方法, 預置門時間為1.5s, 在標準頻率信號為50MHz

28、的情況下, 根據上文討論的高精度恒誤差的頻率和周期測試方法相對誤差計算公式可以算出測量精度為: 1 / ( 1.550106 ) = 1.310-8即能夠顯示接近8位有效數字, 所以電路采用了8位LED顯示器. 如圖3.6所示。圖3.6 八位LED動態顯示器電路 本系統的LED的驅動電流由7片串級的串入并出的移位寄存器74LS164提供,基本可以保證LED的亮度,由工作于同步位移寄存器0模式的串行口輸出顯示數據,用一片74LS164作為顯示單位以及工作狀態的指示,數據與7位顯示串聯,即第8位顯示數據。圖3.7 采用74LS164的動態驅動3.7 實際數字測量部分本設計要求測量功能模塊較多, 設

29、計要求的被測信號以及標準頻率信號為1MHz, 高頻信號之間的信號干擾非常的強. 在方案實現過程中要求處處考慮到干擾問題, 減少布線的復雜程度.各模塊的電路詳細設計如下:3.71 頻率測量與周期測量電路因為本設計采用高精度恒誤差頻率測量法與高精度恒誤差周期測量法, 這兩種方法使用的電路完全相同, 所以在方案實現中, 頻率測量與周期測量使用同一電路, 只是單片機運算不同.頻率測量與周期測量電路由顯示在圖3.3中的控制信號以及以下三個子模塊構成: CONTRL- 本模塊的控制部分, 主要接收單片機的指令, 控制計數器CONT1和CONT2. CONT1- 對由被測信號整形后形成的脈沖進行計數. CO

30、NT2- 對標準頻率信號進行計數.根據高精度恒誤差頻率和周期測量原理, 本模塊電路按以下方式進行工作: 經過整形后的被測信號脈沖從CONTRL的FIN端輸入, 標準頻率信號從CONTRL的FSD端輸入, CONTRL的輸入端是本模塊電路的工作初始化信號輸入端. 在進行頻率或周期測量時, 進行以下幾步:在CONTRL的CLR端加一正脈沖信號以完成測試電路狀態的初始化;由預置門控信號將CONTRL的START端置高電平, 預置門開始定時. 同時由被測信號的上升沿打開計數器CONT1, 并使標準頻率信號被關斷.預置門定時結束信號把CONTRL的START端置為低電平. 這使在被測信號的下一個脈沖的上

31、升沿到來時, CONT1停止計數, 同時輸入CONT2的標準頻率信號被關斷.控制部分CONTRL的EEND端輸出低電平來指示測量計數結束. 單片機讀回CONT1和CONT2的計數值, 根據高精度恒誤差測量公式進行浮點運算, 計算出被測信號的頻率或周期值.3.7.2控制部分設計圖3.8 測頻模塊原理邏輯圖控制部分原理圖如圖3.9所示。當D觸發器的輸入端START為高電平時, 在FIN端來一個上升沿時, Q端為高電平, 導通FIN-CLK1和FSD-CLK2, 同時EEND被置為高電平; 在D觸發器的輸入端START為低電平時, 當FIN端輸入一個脈沖上升沿, FIN-CLK1和FSD-CLK2的

32、信號通道被切斷.圖3.8中的計數器CONT1是用8個四位并行二進制計數器按行波計數器原理所構成的32位二進制計數器, 輸出8位數據總線, 分4次將32位數據全部讀出. CONT1的設計是用VHDL語言實現的.我們在EDA設計中嚴格采用模塊設計法, 總體設計采用原理圖輸入方式, 每個子模塊都采用VHDL語言描述.3.7.3脈沖寬度測量和占空比測量電路圖3.9 測頻率與測周期部分控制電路本模塊的電路設計根據第二部分所述的脈沖寬度測量原理, 設計如圖3.5的電路原理圖.輸入到本模塊的被測量信號是經過信號處理電路處理過后的被測信號, 該信號的上升沿和下降沿信號對應于未經處理時的被測信號的50%幅度時上

33、升沿和下降沿信號.信號從FIN端輸入, CLR為本模塊電路的工作初始化信號輸入端. START為本電路的工作使能端, PUL端輸出如圖3.8中所示GATE的輸入端PUL.測量脈沖寬度采用以下幾步:向CONTRL2的CLR端輸送一個脈沖以進行電路的工作狀態初始化.將圖3.8中GATE的T端置為高電平, 表示進入脈沖寬度測量, 這時CONT2的輸入信號為PUL&FSD.在經過處理后的被測信號的上升沿到來之時, CONTRL2的PUL端輸出高電平, 標準頻率信號進入計數器CONT2.在經過處理后的被測信號的下降沿到來之時, CONTRL2的PUL端輸出低電平, 計數器CONT2被關斷.單片機讀計數器

34、CONT2的結果, 通過所述的測量原理公式(2.8)計算得出脈沖寬度.占空比的測量方法是通過測量脈沖寬度記錄CONT2的計數值Twx1, 然后將輸入信號反相, 再測量其脈沖寬度, 測得CONT2計數值Twx2, 則可以計算出占空比 = Twx1100% / (Twx1+Twx2)圖3.10 脈沖測量模塊邏輯原理圖第4章單片機控制與運算程序的設計4.1 單片機控制與運算的主流程圖調測脈寬子程序置標志位 有鍵按下嗎清標志位調測周期子程序置標志位 有鍵按下嗎調測頻子程序是測占空比鍵嗎 是測脈寬鍵嗎 是測周期鍵嗎 開始 清內存SP 60HP2 0 是測頻鍵嗎 有鍵按下嗎調顯示子程序CHOICE 1 1

35、1 清顯示緩沖區, 送初始顯示內容 清標志位 有鍵按下嗎置標志位測占空比子程序清標志位有鍵按下嗎圖4.1 單片機控制與運算主流程圖4.2 VHDL源程序-T10.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ENTITY T10 IS PORT (CLK:IN STD_LOGIC; CLR:IN STD_LOGIC; ENA:IN STD_LOGIC; CQ:OUT INTEGER RANGE 0 TO 15; CARRY_OUT:OUT STD_LOGIC); END ENTITY T10;ARCHITECTURE ART OF T10 IS SI

36、GNAL CQI :INTEGER RANGE 0 TO 15;BEGINPROCESS(CLK,CLR,ENA) ISBEGINIF CLR=1 THEN CQI=0; ELSIF CLKEVENT AND CLK=1 THEN IF ENA=1 THEN IF CQI9 THEN CQI=CQI+1; ELSE CQI=0; END IF; END IF;END IF;END PROCESS;PROCESS (CQI) ISBEGINIF CQI=9 THEN CARRY_OUT=1; ELSE CARRY_OUT=0;END IF;END PROCESS; CQ=CQI;END ARCH

37、ITECTURE ART;-REG32B.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY REG32B IS PORT(LOAD:IN STD_LOGIC; DIN:IN STD_LOGIC_VECTOR(31 DOWNTO 0); DOUT:OUT STD_LOGIC_VECTOR(31 DOWNTO 0);END ENTITY REG32B;ARCHITECTURE ART OF REG32B IS BEGINPROCESS(LOAD,DIN)ISBEGINIF LOADEVENT AND LOAD=1 THEN DOUT=DIN; E

38、ND IF;END PROCESS;END ARCHITECTURE ART;-TESTCTL.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY TESTCTL IS PORT (CLK:IN STD_LOGIC; TSTEN:OUT STD_LOGIC; CLR_T:OUT STD_LOGIC; LOAD:OUT STD_LOGIC); END ENTITY TESTCTL;ARCHITECTURE ART OF TESTCTL IS SIGNAL DIV2CLK: STD_

39、LOGIC;BEGINPROCESS(CLK)ISBEGIN IF CLKEVENT AND CLK= 1 THEN DIV2CLK=NOT DIV2CLK; END IF ;END PROCESS;PROCESS(CLK,DIV2CLK) ISBEGIN IF CLK=0 AND DIV2CLK=0 THEN CLR_T=1; ELSE CLR_T=0; END IF;END PROCESS; LOAD=NOT DIV2CLK; TSTEN=DIV2CLK;END ARCHITECTURE ART;-display.vhdlibrary ieee;use ieee.std_logic_116

40、4.all;use ieee.std_logic_unsigned.all;entity display isport(clk:in std_logic; dout:in std_logic_vector(31 downto 0); :out std_logic_vector(2 downto 0); seg:out std_logic_vector(7 downto 0);end entity display;architecture art of display is signal t:std_logic_vector(2 downto 0); signal bcd:std_logic_v

41、ector(3 downto 0); beginprocess(clk) begin if clkevent and clk=1 then if t=111 then t=000; else t=t+1; end if; end if;end process; bcdbcdbcdbcdbcdbcdbcdbcdbcdsegsegsegsegsegsegsegsegsegsegsegsegsegsegsegsegsegCLK,TSTEN=SE,CLR_T=SC,LOAD=SL);U1:T10 PORT MAP(CLK=FSIN,CLR=SC,ENA=SE,CQ=SD(3 DOWNTO 0),CARRY_OUT=S1); U2:T10 PORT MAP(CLK=S1,CLR=SC,ENA=SE,CQ=SD(7 DOWNTO 4),CARRY_OUT=S2);U3:T10 PORT MAP(S2,SC,SE,SD(11 DOWNTO 8 ),S3);U4:T10 PORT MAP(S3,SC,SE,SD(15 DOWNTO 12),S4);U5:T10 PORT MAP(S4,SC,SE,SD(19 DOWNTO 16),S5);U6:T10 PORT MAP(S5,SC,SE,SD(23 DOWNTO 20),S6);U7:T10 PORT MAP(S6,SC,S

溫馨提示

- 1. 本站所有資源如無特殊說明,都需要本地電腦安裝OFFICE2007和PDF閱讀器。圖紙軟件為CAD,CAXA,PROE,UG,SolidWorks等.壓縮文件請下載最新的WinRAR軟件解壓。

- 2. 本站的文檔不包含任何第三方提供的附件圖紙等,如果需要附件,請聯系上傳者。文件的所有權益歸上傳用戶所有。

- 3. 本站RAR壓縮包中若帶圖紙,網頁內容里面會有圖紙預覽,若沒有圖紙預覽就沒有圖紙。

- 4. 未經權益所有人同意不得將文件中的內容挪作商業或盈利用途。

- 5. 人人文庫網僅提供信息存儲空間,僅對用戶上傳內容的表現方式做保護處理,對用戶上傳分享的文檔內容本身不做任何修改或編輯,并不能對任何下載內容負責。

- 6. 下載文件中如有侵權或不適當內容,請與我們聯系,我們立即糾正。

- 7. 本站不保證下載資源的準確性、安全性和完整性, 同時也不承擔用戶因使用這些下載資源對自己和他人造成任何形式的傷害或損失。

最新文檔

- PPP模式合同標準文本 - 修訂版

- 2025技術人員雇傭合同

- 2025年超市貨物采購合同范本

- 2025年城市個人租房合同范本

- 2025建筑工地安保服務合同模板

- 2025合同履行中的終止權

- 2025建筑工程分包合同模板

- 2025年的產權轉讓委托合同樣本

- 2025年反擔保合同協議樣本

- 《培訓的組織與實施》課件

- 2025年內蒙古赤峰新正電工技術服務有限公司招聘筆試參考題庫含答案解析

- 2024-2025學年七年級下學期期中英語模擬試卷(深圳專用)(解析版)

- 競業及保密協議

- 船舶防汛應急預案

- 2024年司法考試歷年真題答案

- 2025年南昌市高三語文二模檢測試卷附答案解析

- 2025年03月湖南懷化市新晃侗族自治縣事業單位工作人員10人筆試歷年典型考題(歷年真題考點)解題思路附帶答案詳解

- DB32-T 5085-2025 無機涂料應用技術規程

- 林海雪原考試題和答案

- 2025年中國華電集團有限公司招聘筆試參考題庫含答案解析

- 語文版一年級下冊語文閱讀理解練習(15篇)

評論

0/150

提交評論