版權說明:本文檔由用戶提供并上傳,收益歸屬內容提供方,若內容存在侵權,請進行舉報或認領

文檔簡介

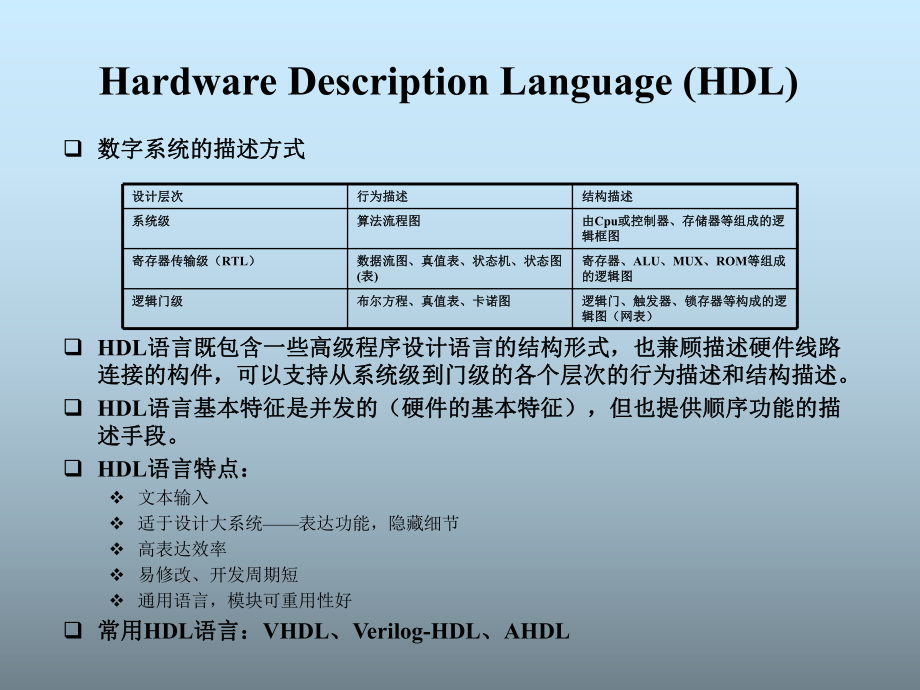

1、可編程邏輯電路設計教學組可編程邏輯電路設計教學組二二七年七年Hardware Description Language (HDL)q 數字系統的描述方式數字系統的描述方式q HDL語言既包含一些高級程序設計語言的結構形式,也兼顧描述硬件線路語言既包含一些高級程序設計語言的結構形式,也兼顧描述硬件線路連接的構件,可以支持從系統級到門級的各個層次的行為描述和結構描述。連接的構件,可以支持從系統級到門級的各個層次的行為描述和結構描述。q HDL語言基本特征是并發的(硬件的基本特征),但也提供順序功能的描語言基本特征是并發的(硬件的基本特征),但也提供順序功能的描述手段。述手段。q HDL語言特點:語

2、言特點:v 文本輸入v 適于設計大系統表達功能,隱藏細節v 高表達效率v 易修改、開發周期短v 通用語言,模塊可重用性好q 常用常用HDL語言:語言:VHDL、Verilog-HDL、AHDL 設計層次設計層次行為描述行為描述結構描述結構描述系統級系統級算法流程圖算法流程圖由由Cpu或控制器、存儲器等組成的邏或控制器、存儲器等組成的邏輯框圖輯框圖寄存器傳輸級(寄存器傳輸級(RTL)數據流圖、真值表、狀態機、狀態圖數據流圖、真值表、狀態機、狀態圖(表表)寄存器、寄存器、ALU、MUX、ROM等組成等組成的邏輯圖的邏輯圖邏輯門級邏輯門級布爾方程、真值表、卡諾圖布爾方程、真值表、卡諾圖邏輯門、觸發器

3、、鎖存器等構成的邏邏輯門、觸發器、鎖存器等構成的邏輯圖(網表)輯圖(網表)VHDL語言語言q Very high speed integrated circuit HDLq IEEE工業標準工業標準HDL語言語言q 可支持仿真與綜合可支持仿真與綜合q 兩個版本:兩個版本:v 10761987v 10761993VHDL程序結構程序結構q 1、USE定義區定義區v Library定義所使用的元件庫v Package定義所使用的元件庫中的包q 2、Entity定義區:定義電路實體的定義區:定義電路實體的I/O接口規格接口規格q 3、Architecture定義區:描述電路內部具體功能定義區:描述電

4、路內部具體功能v Component定義區v 信號定義v 行為描述/數據流描述/結構描述q 4、Configuration定義區:決定使用哪一個定義區:決定使用哪一個architecture(非必須)(非必須)Use定義區定義區Library IEEE;-庫定義庫定義Use IEEE.std_logic_1164.all;-包引用包引用Use IEEE.std_logic_arith.all;-包引用包引用引用語句的用法:引用語句的用法:Library ,;Use lib_name.pack_name.object;PackagesPackage isConstant Decclaration

5、sType DeclarationsSignal DeclarationsSubprogram DeclarationsComponent DeclarationsOther DeclarationsEnd ;(1076-1987)End Package ;(1076-1993)Package Body isConstant DeclarationsType DeclarationsSubprogram BodyEnd Package ;(1076-1987)End Package Body (1076-1993)Package Examplepackage package_example i

6、stype life is (sleeping, working, eating, entertaiment, otheractions);subtype uint4 is integer range 0 to 15;subtype uint5 is integer range 0 to 31;function compare(a, b: integer) return boolean;end package_example;package body package_example isfunction compare(a,b: integer) return boolean isvariab

7、le temp:boolean;beginif ab thentemp:=true;elsetemp:=false;end if;return temp;end compare;end package_example;Librariesq 包括一系列的包括一系列的packagesq 隱含隱含Libraries: 不用聲明,自動引用不用聲明,自動引用v STD: Standard:定義bit, Boolean, integer, real和time以及支持它們的運算符。 Textio:定義文件操作。v Work: v IEEE: Std_logic_1164 Std_logic_arith St

8、d_logic_signed Std_logic_unsignedv 其它庫: Altera的元件庫 用戶自定義庫Entity(實體)(實體)q Entity定義語法Entity isgeneric declarationsport declarationsEnd ;q Entity ExampleEntity adder isgeneric(data_width:integer:=4 );port( add_a, add_b: in std_logic_vector(data_width-1 downto 0);sum: out std_logic_vector(data_width dow

9、nto 0) );End adder;Generic & Port Declarationsq Generic Declarationsv 用于將參數傳入Entity。例如:數據線寬度,器件的延時參數、負載電容電阻、驅動能力、功耗等等。q Port Declarations: port_name: : v :管腳的模式 In (輸入) Out (輸出) Buffer (輸出帶內部反饋) Inout (雙向)v : 數據類型 Boolean: False, True Bit: 0, 1 Std_logic: X, 0, 1, Z, -, W, L, H,支持多信號判決 Std_ulogi

10、c: 與Std_logic類型一樣,不支持多信號判決 Bit_vector & std_logic_vector: Integer: NaturalPositive Real: time 自定義數據類型:如數組等Architecture(結構體)(結構體)q 描述設計的功能或者結構描述設計的功能或者結構q 必須與某個必須與某個entity相聯系相聯系q 一個一個entity可以對應多個可以對應多個architecture(編譯時通過編譯時通過configuration來指定來指定)q Architecture中的各個語句是并發執行的,對應于電路硬中的各個語句是并發執行的,對應于電路硬件

11、中的不同部件件中的不同部件q Architecture的描述風格的描述風格v 行為描述描述實體的功能,RTL級 算法描述 數據流描述v 結構描述描述實體的結構,門級v 混合描述Architecture組成組成q Architecture定義定義ARCHITECTURE arch_name OF entity_name ISsignal declarations;constant declarations;type & subtype declarations;component declarations;subprogram declarations;BEGINProcess Stat

12、ements;Concurrent Procedure Calls;Concurrent Signal Assignment;Conditional Signal Assignment;Selected Signal Assignment;Component Instantiation Statements;Generate Statements;END arch_name;結構描述例子結構描述例子半加器半加器Architecture struct_ha of half_adder iscomponent and_gate port( a1,a2: in std_logic; a3: out

13、std_logic);end component;component xor_gate port( a1,a2: in std_logic; a3: out std_logic);end component;Beging1: and_gate port map(a,b,c);g2: xor_gate port map(a,b,s);End struct_ha;行為描述例子行為描述例子半加器半加器q 算法描述算法描述Architecture behave_ha of half_adder isBegin g1:process(a,b)begin if a=1 and b=1 thenc=1; e

14、lsec=0; end if;end process; g2:process(a,b)begin if a=1 and b=0 thenc=1; elsif a=0 and b=1c=1; elsec=0; end if;end process;End struct_ha;q 數據流描述數據流描述Architecture behave_ha of half_adder isBeginc= a and b;s=a xor b;End struct_ha;Configurationq 用于將用于將entity和和architecture聯系起來聯系起來q 廣泛應用于仿真環境廣泛應用于仿真環境q 被

15、綜合器有限支持或者不支持被綜合器有限支持或者不支持q 語法:語法:Configuration of isfor end for;End;數據對象數據對象q Constant(常數常數)v 定義語法: Constant : := v 用符號代表常數,增加程序的可讀性和可維護性v 一經定義,不得更改q Signal(信號信號)v 定義語法: Signal : := v 對應于電路中的某一節點v 通常定義于entity、architecture或者package中,全局使用v 可再賦值 : “ =”v 進程中對信號的賦值在該進程結尾才生效q Variable(變量變量)v 定義語法: Variabl

16、e : :=v 不對應于具體電路中的節點,一般用于計算用途v 只局限于進程和子程序中定義并使用v 可再賦值: “:=”v 對變量的賦值立即生效信號和變量的區別信號和變量的區別例例1q一段程序:a, b: in std_logic;x, y: out std_logic;signal temp: std_logic;process (a, b, temp)begintemp=a;x=temp;temp=b;y=temp;end process;q等價電路圖:q另一段程序:a, b: in std_logic;x, y: out std_logic;process (a, b, temp) var

17、iable temp: std_logic;begintemp:=a;x=temp;temp:=b;y=temp;end process;q等價電路圖:信號和變量的區別信號和變量的區別例例2q一段程序:D, clk: in std_logic;x: out std_logic;signal temp: std_logic;process (clk)begin if (clkevent and clk=1) thentemp=D;x=temp; end if;end process;q等價電路圖:q另一段程序:D, clk: in std_logic;x: out std_logic;proce

18、ss (clk) variable temp: std_logic; begin if (clkevent and clk=1) thentemp:=D;x=temp; end if;end process;q等價電路圖:數據類型數據類型q 基本數據類型基本數據類型v 邏輯類型: bit, boolean, std_logic, std_ulogic, std_logic_vector, bit_vectorv 整數類型: Integer(及其子類如Natural, Positive), unsigned, signedv 實數類型: Realq 高級數據類型高級數據類型v 枚舉類型: 定義語

19、法:TYPE IS (, , ) 使程序易讀,例如在定義狀態機時v 數組類型: 定義語法:TYPE IS ARRAY (integer1 DOWNTO integer2) OF 多用于定義ROM、RAM等運算符運算符q 關系運算符:關系運算符:v = = = /=q 邏輯運算符:邏輯運算符:v and, or, not, nand, nor, xorq 算術運算符:算術運算符:v * / MOD REM * ABSq 其他運算符:其他運算符:v (正號) (負號) &(連接) q 運算符重載運算符重載v 對于不同的數據類型定義同樣一個運算,其實際操作可能不同。例如+(加)運算,可以對整

20、數使用,也可以對std_loigc_vector等類型用(在std_logic_arith包中定義)。v 通常定義與package中。v IEEE的package中定義了大量的重載運算符Vector信號的分解與合并信號的分解與合并Architecture rtl of test issignal a: std_logic_vector(3 downto 0);signal b: std_logic_vector(0 to 3);signal c: std_logic_vector(0 to 1);signal d: std_logic_vector(1 downto 0);Beginc=a(2

21、 downto 1);b=A(3) & D & 1End rtl;a(3)a(2)a(1)a(0)b(0)b(1)b(2)b(3)c(0) d(1)c(1) d(0)1并發語句并發語句q VHDL程序的結構體中的各個語句是并發的,代表電路程序的結構體中的各個語句是并發的,代表電路的不同節點,它們是同時運作的的不同節點,它們是同時運作的q 并發語句的順序不影響其執行結果并發語句的順序不影響其執行結果q 并發語句列表:并發語句列表:v 直接信號賦值: =v 條件信號賦值:when-elsev 選擇信號賦值:selectwhenv 進程:processv 斷言:assert面向仿真的

22、語句,不能綜合v 塊語句:Blockv Component語句v For-GenerateWhen-elseq 語法:語法: = when else when else. when else ;q 特點:特點:v 各個條件可以不互斥v 主要用于譯碼器、多路復接器和解復接器q 例子:例子: q = a when sel=“00” elseb when sel=“01” elsec when sel=“10” elsed;abcdselqSelect-whenq 語法:語法:with select = when , when ,. when others;q 特點:特點:v 各個條件必須互斥v 主

23、要用于譯碼器、多路復接器和解復接器q 范例:范例: with sel selectq = a when “00”,b when “01”,c when “10”,d when others;abcdselqBlockq 用于將電路劃分成幾個模用于將電路劃分成幾個模塊,增加程序的可讀性塊,增加程序的可讀性q 語法:語法: blockBeginEnd block ;q 范例:范例:Library ieee;Use ieee.std_logic_1164.all;Entity half_addsub isport(a,b: in std_logic;sum, carry: out std_logic

24、;diff, borrow: out std_logic);End half_addsub;Architecture rtl of half_addsub isBeginHalf_adder: blocksum=a xor b;carry=a and b;End block half_adder;Half_sub: blockdiff=a xor b;borrow=(not a) and b;End block half_sub;End rtl;Componentq Component定義語句:與定義語句:與entity類似類似 Component generic ( generic_decl

25、arations );port ( port_declarations);End component;q Component例化語句:例化語句:: generic map ( generic_mapping)port map (port_mapping);q Port map語句兩種格式:語句兩種格式:v Port map ( =, =, );v Port map ( , , ); Component范例范例4位全加器位全加器Library ieee;Use ieee.std_logic_1164.all;Entity full_adder_4 isport( A, B: in std_log

26、ic_vector(3 downto 0); ci: in std_logic; C: out std_logic_vector(3 downto 0); co: out std_logic);End full_adder_4;Architecture rtl of full_adder_4 iscomponent full_adder_1port(a,b: in std_logic;ci: in std_logic;c: out std_logic;co: out std_logic);end component;signal t: std_logic_vector(2 downto 0);

27、BeginU0: full_adder_1port map(A(0),B(0),ci,C(0),t(0);U1: full_adder_1port map(A(1),B(1),t(0),C(1),t(1);U2: full_adder_1port map(A(2),B(2),t(1),C(2),t(2);U3: full_adder_1port map(A(3),B(3),t(2),C(3),co);End rtl;ciFull_adder_1A(0) B(0)Full_adder_1t(0)A(1) B(1)Full_adder_1t(1)A(2) B(2)Full_adder_1t(2)A

28、(3) B(3)coC(0)C(1)C(2)C(3)For-Generateq 例化多個相同的例化多個相同的Componentq 語法:語法:: For i in to generatecomponent例化語句;End generate ;q 范例范例: 4位全加器位全加器Architecture rtl of full_adder_4 is;signal t: std_logic_vector(4 downto 0);Begingen: for I in 0 to 3 generateadd1: full_adder_1 port map(A(i),B(i),t(i),C(i),t(i+1

29、);end generate gen;t(0)=ci;co=t(4);End rtl;q If-Generate語句可以條件生成。語句可以條件生成。q 生成語句可以嵌套。生成語句可以嵌套。順序語句順序語句q 可用于進程、函數和子程序中可用于進程、函數和子程序中q 依次執行,語句順序影響其執行結果依次執行,語句順序影響其執行結果q 順序語句的執行需要被激活順序語句的執行需要被激活q 順序語句列表:順序語句列表:v 變量和信號賦值::= =v If語句:if-then-elsif-elsev Case語句:case-whenv Loop語句v Wait語句Processq 特點:特點:v Proc

30、ess語句本身是一個并發式語句,但其內部包含的是順序語句v 僅當進程的某個敏感信號發生變化時,進程內部的順序語句塊才被激活依次執行;否則進程處于被掛起的狀態。v 進程內的變量在進程被掛起和再次激活時,保持原值。v 可以通過兩種方式定義敏感信息:用敏感信息表或者用wait語句。但這兩者不能同時出現在一個進程中(wait語句可以有多個)。q 定義語法:定義語法:Process()constant declaration;type declarations;variable declarations;Beginsequential statement #1;sequential statement

31、#2; .sequential statement #n;End process;Process范例范例Process(clk)Beginif (clkevent and clk=1) thenq=d;end if;End process;ProcessBeginwait on clk;if clkevent and clk=1 thennq=not d;end if;End process;Process敏感列表敏感列表(1)正常的代碼Process (ck, d)Beginif ck=1 thenq=d;end if;End process;Max+plus II綜合結果:LatchFPG

32、A Express綜合結果: Latch(2)危險的代碼Process (ck)Beginif ck=1 thenq=d;end if;End process;Max+plus II綜合結果: D觸發器FPGA Express綜合結果: LatchIf語句語句q 語法:語法:If thensequential statements;Elsif thensequential statements; .Elsesequential statements;End if;q 對應于對應于when-else語句語句q 范例范例:if sel=“00” thenq=a;elsif sel=“01” the

33、nq=b;elsif sel=“10” thenq=c;elseq=d;end if;Case語句語句q 語法:語法:case is when =sequential statements; when =sequential statements; . when others=sequential statements;end case;q 對應于對應于select-when語句語句q 范例范例:case sel is when “00” =q q q q=d;end case;Loop語句語句q 無限循環:使用無限循環:使用Exit退出循環退出循環v 語法:: Loopsequential

34、statements;exit Loop_lable when ;End loop;q While循環:根據條件結束循環循環:根據條件結束循環While Loopsequential statements;End loop;q For循環:循環:FOR IN Loopsequential statements;End loop;Loop語句范例語句范例q 例1Signal a: std_logic_vector(7 downto 0)Process (a)variable temp: std_logic;Begintemp:=1;for I in 0 to 7 loop temp:=temp

35、and a(i);end loop;b=temp;End process;q 例2Signal a: std_logic_vector(7 downto 0)Process (a)variable cnt: integer;variable temp: std_logic;Begintemp:=1;cnt=0;while cnt8 loop temp:=temp and a(cnt); cnt:=cnt+1;end loop;b=temp;End process;SubprogramPackage body of example is procedure p(A: in integer, B:

36、inout integer) is begin B:=A+B; end; function inc(A: in integer) return integer is beginreturn (A+1) end;End example; q 子程序調用范例:子程序調用范例:p(a,b);x=inc(a); q 用于描述一定的算法用于描述一定的算法q 內部是串行執行內部是串行執行類似類似processq 可以在程序中任何地方被調用可以在程序中任何地方被調用q 調用方法類似于調用方法類似于Component例例化化q 綜合結果是組合邏輯電路綜合結果是組合邏輯電路q 包括包括function和和procedurev Function: 有返回值v Procedure: 無返回值q 子程序定義范例:子程序定義范例:Package example is procedure p(A: in integer, B:inout integ

溫馨提示

- 1. 本站所有資源如無特殊說明,都需要本地電腦安裝OFFICE2007和PDF閱讀器。圖紙軟件為CAD,CAXA,PROE,UG,SolidWorks等.壓縮文件請下載最新的WinRAR軟件解壓。

- 2. 本站的文檔不包含任何第三方提供的附件圖紙等,如果需要附件,請聯系上傳者。文件的所有權益歸上傳用戶所有。

- 3. 本站RAR壓縮包中若帶圖紙,網頁內容里面會有圖紙預覽,若沒有圖紙預覽就沒有圖紙。

- 4. 未經權益所有人同意不得將文件中的內容挪作商業或盈利用途。

- 5. 人人文庫網僅提供信息存儲空間,僅對用戶上傳內容的表現方式做保護處理,對用戶上傳分享的文檔內容本身不做任何修改或編輯,并不能對任何下載內容負責。

- 6. 下載文件中如有侵權或不適當內容,請與我們聯系,我們立即糾正。

- 7. 本站不保證下載資源的準確性、安全性和完整性, 同時也不承擔用戶因使用這些下載資源對自己和他人造成任何形式的傷害或損失。

最新文檔

- 詩歌鑒賞|沈佺期《夜宿七盤嶺》注釋+賞析+試題

- 2025年保險箱執手行業深度研究報告

- 合同能源管理中介合同

- 2025-2030年全球及中國工業廢物回收及服務行業市場現狀供需分析及投資評估規劃分析研究報告

- 智能交通信號控制系統合同

- 電影版權侵權賠償合同

- 裝修抵房租合同

- 機電工程服務合同

- 技術合同延期協議書

- 成渝云簽合同協議書

- 結合工作實際談如何改進工作作風、提高工作效率、改進工作方法六篇

- 醫院醫學倫理委員會相關表格模版(共3個)

- 道德與法治一年級下冊《大家一起來合作》教學設計

- 中國傳統故事英文十二生肖二篇

- ETL認證的工廠審查

- 基本醫療保險異地就醫備案個人承諾書

- 中國古代文學史 馬工程課件(下)05第七編明代文學 第四章 《水滸傳》

- YC/T 215-2007煙草行業聯運通用平托盤

- JJF 1751-2019菌落計數器校準規范

- 威尼斯商人英文劇本(法庭)

- (出讓合同)國有建設用地使用權先租后讓合同范本

評論

0/150

提交評論