版權說明:本文檔由用戶提供并上傳,收益歸屬內容提供方,若內容存在侵權,請進行舉報或認領

文檔簡介

1、EDA課程設計多路彩燈控制設計前言本次課程設計的主要目的是通過電子設計自動化的設計,掌握FPGA應用系統的開發過程,進一步理解FPGA應用系統的工作原理。本課程設計設計了一個多路彩燈控制器,十六種彩燈能循環變化,有清零開關,可以變化彩燈閃動頻率即是可以選擇快慢兩種節拍。整個系統有三個輸入信號,分別為控制快慢的信號OPT,復位清零信號CLR,輸出信號是16路彩燈輸出狀態。最后按照FPGA的開發流程和VHDL語言建模、仿真、綜合、下載、適配,用EDA6000實驗箱上的FPGA系統實現了相應的功能。通過這次課程設計更清楚的理解了VHDL程序的描述語言,能進行簡單程序的編寫和仿真。一系統設計要求 設計

2、一個多路彩燈控制器,十六種彩燈能循環變化,有清零開關,可以變化彩燈閃動頻率即是可以選擇快慢兩種節拍。二.設計方案整個系統有三個輸入信號,分別為控制快慢的信號OPT,復位清零信號CLR,輸出信號是16路彩燈輸出狀態。系統框圖如: 主要模塊組成:時序控制電路模塊和顯示電路模塊,時序控制電路是根據輸入信號的設置得到相應的輸出信號,并將此信號作為顯示電路的時鐘信號;顯示電路輸入時鐘信號的周期,有規律的輸出設定的六種彩燈變化類型。三.模塊設計時序控制模塊:CLK_IN為輸入時鐘信號,電路在時鐘上升沿變化;CLR為復位清零信號,高電平有效,一旦有效時,電路無條件的回到初始狀態;chose_key為頻率快慢

3、選擇信號,低電平節奏快,高電平節奏慢;CLK為輸出信號,CLR有效時輸出為零,否則,隨chose_key信號的變化而改變。我們假設時序控制電路所產生的控制時鐘信號的快慢兩種節奏分別為輸入時鐘信號頻率的1/4和1/8,因而輸出時鐘控制信號可以通過對輸入時鐘的計數來獲得。當chose_key為低電平時,輸出沒經過兩個時鐘周期進行翻轉,實現四分頻的快節奏;當chose_key為高電平時,輸出每經過四個時鐘周期進行翻轉,實現把八分頻的慢節奏。顯示控制電路的模塊框圖如圖所示,輸入信號clk和的定義與時序控制電路一樣,輸入信號led15.0能夠循環輸出16路彩燈16種不同狀態的花型。對狀態的所對應的彩燈輸

4、出花型定義如下:S0:0000000000000000 S1:多路彩燈在多種花型之間的轉換可以通過狀態機實現,當復位信號clr有效時,彩燈恢復初始狀態s0,否則,每個時鐘周期,狀態都將向下一個狀態發生改變,并對應輸出的花型,這里的時鐘周期即時時序控制電路模塊產生的輸出信號,它根據chose_key信號的不同取值得到兩種快慢不同的時鐘頻率。四.序控制電路模塊程序如下:Library ieee; Use ieee.std_logic_1164.all; Use ieee.std_logic_unsigned.all; Entity CD is Port(chose_key1:in std_logi

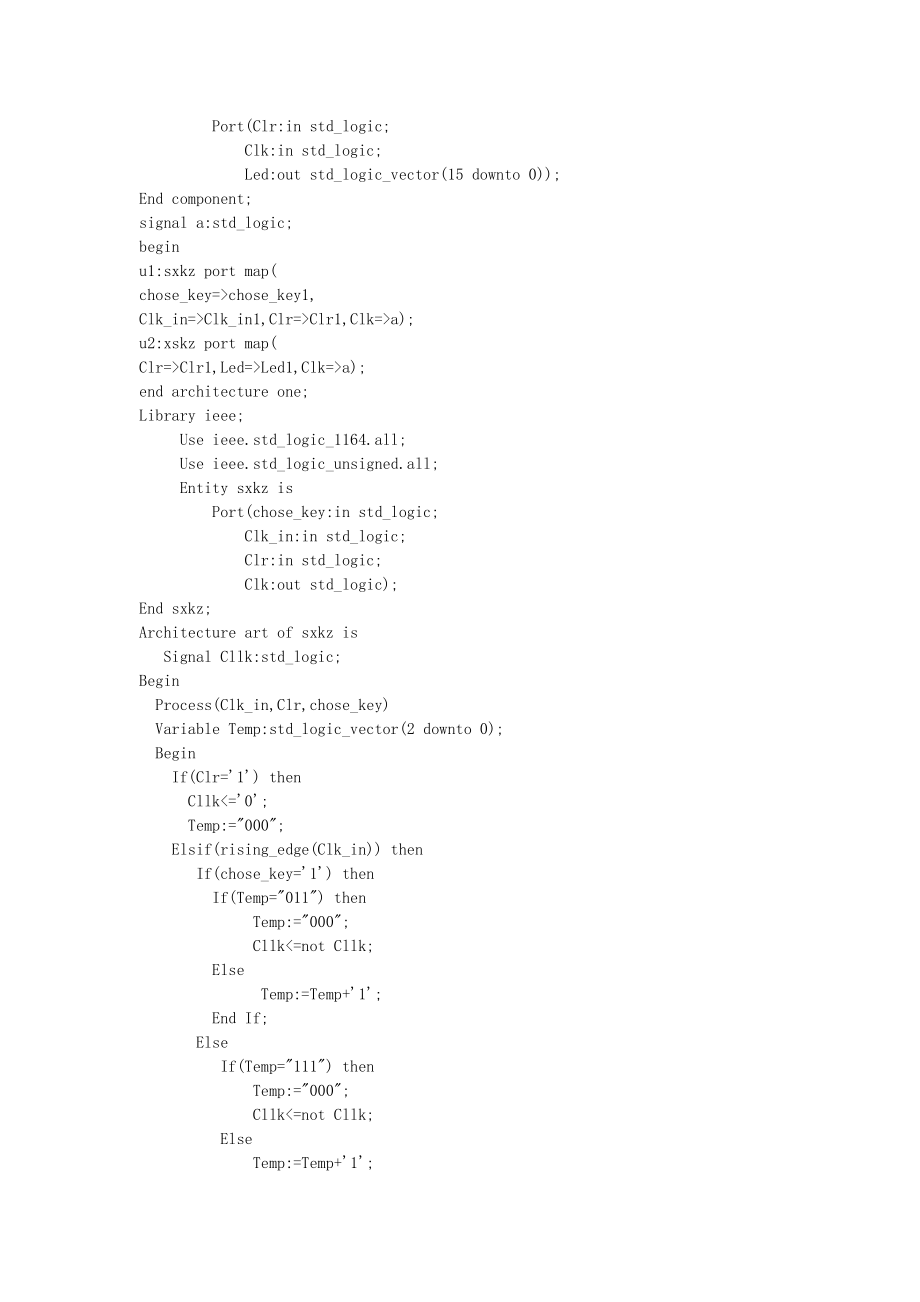

5、c; Clk_in1:in std_logic; Clr1:in std_logic; Led1:out std_logic_vector(15 downto 0); End CD; Architecture one of CD iscomponent sxkzPort(chose_key:in std_logic; Clk_in:in std_logic; Clr:in std_logic; Clk:out std_logic);End component; component xskz Port(Clr:in std_logic; Clk:in std_logic; Led:out std

6、_logic_vector(15 downto 0);End component;signal a:std_logic;beginu1:sxkz port map(chose_key=>chose_key1,Clk_in=>Clk_in1,Clr=>Clr1,Clk=>a);u2:xskz port map(Clr=>Clr1,Led=>Led1,Clk=>a);end architecture one;Library ieee; Use ieee.std_logic_1164.all; Use ieee.std_logic_unsigned.all;

7、 Entity sxkz is Port(chose_key:in std_logic; Clk_in:in std_logic; Clr:in std_logic; Clk:out std_logic);End sxkz;Architecture art of sxkz is Signal Cllk:std_logic;Begin Process(Clk_in,Clr,chose_key) Variable Temp:std_logic_vector(2 downto 0); Begin If(Clr='1') then Cllk<='0' Temp:=

8、"000" Elsif(rising_edge(Clk_in) then If(chose_key='1') then If(Temp="011") then Temp:="000" Cllk<=not Cllk; Else Temp:=Temp+'1' End If; Else If(Temp="111") then Temp:="000" Cllk<=not Cllk; Else Temp:=Temp+'1' End If; End

9、 If; End If; End process; Clk<=Cllk; End art;Library ieee;Use ieee.std_logic_1164.all; Use ieee.std_logic_unsigned.all; Entity xskz is Port( Clr:in std_logic; Clk:in std_logic; Led:out std_logic_vector(15 downto 0);End xskz;Architecture art of xskz is Type state is(s0,s1,s2,s3,s4,s5,s6,s7,s8,s9,s

10、10,s11,s12,s13,s14,s15,s16); Signal current_state:state; Signal flower:std_logic_vector(15 downto 0); Begin Process(Clr,Clk) Begin If(Clr='1') then current_state<=s0; elsif(rising_edge(Clk) then case current_state is when s0=> flower<="ZZZZZZZZZZZZZZZZ" current_state<=s

11、1; when s1=> flower<=f1; current_state<=s2; when s2=> flower<=f2; current_state<=s3; when s3=> flower<=f3; current_state<=s4; when s4=> flower<=f4; current_state<=s5; when s5=> flower<=f5; current_state<=s6; when s6=> flower<=f6; current_state<=s

12、7; when s7=> flower<=f7; current_state<=s8; when s8=> flower<=f8; current_state<=s9; when s9=> flower<=f9; current_state<=s10; when s10=> flower<=f10; current_state<=s11; when s11=> flower<=f11; current_state<=s12; when s12=> flower<=f12; current_st

13、ate<=s13; when s13=> flower<=f13; current_state<=s14; when s14=> flower<=f14; current_state<=s15; when s15=> flower<=f15; current_state<=s16; when s16=> flower<=f16; current_state<=s1; end case; end if; end process; led<=flower; end art;時序模塊電路程序如下:顯示模塊電路程序:頂

14、出模塊設計程序:其狀態圖:時序控制模塊仿真波形:從圖中可以看出,當復位信號為高電平時,電路時鐘輸出清零,當快慢信號chose_key1為低電平時,時序控制電路四分頻起作用,當快慢信號chose_key1為高電平時,時序控制電路八分頻起作用,仿真結果符合電路要求。顯示模塊仿真波形:當復位信號有效時彩燈輸出為零,否則,顯示電路在十六種不同狀態間轉換。多路彩燈控制仿真波形:從圖中可以看出當chose_key1為高電平時彩燈狀態轉換慢,為低電平時轉換要快,當復位信號有效時,所用輸出都清零。偉福6000仿真圖:綜上所述,本次設計實現了設計要求中的要求。五.系統設計工作進程安排: 17周 周一、二,查找和

15、準備了相關設計材料,熟悉過去學過的FPGA芯片、VHDL 語言和EDA環境相關知識 周三、四、五,進行相應的程序設計 18周 周一,在實驗室熟悉EDA的環境使用,熟悉相關設計軟件 周二、三,在實驗室上機,使用EDA6000實驗箱調試程序 周四,老師驗收設計六.心得體會本次設計的課題是彩燈控制器的設計,當拿到這個課題的時候經過分析就知道關鍵是計數器和分頻器的使用,分頻的方法有很多種,對于同一種功能的實現,用VHDL可以采用多種方式進行描述,每種方式之間各有優劣,本次設計只采用了其中較簡單的一種,應盡量用最簡潔的語言寫出所需功能的程序。通過這次課程設計對技術有了更進一步的熟悉,VHDL 語言和語言

16、等其他語言還是有很大的區別。VHDL是EDA技術的重要組成部分,其具有與具體硬件電路無關和與設計平臺無關的特性,并且具有良好的電路行為描述和系統描述的能力,并在語言易讀性和層次化、結構化設計方面,表現了強大的生命力和應用潛力。其主要的也是最大的優點就在于設計者可以專心致力于其功能的實現,而不需要對不影響功能的與工藝有關的因素花費過多的時間和精力。在實際操作中發現設計和課本上的知識有很大聯系,但又高于課本,一個簡單的原理要把它應用以及和其他功能綜合起來就有些困難。通過設計也鞏固了我們的書本知識以及通過借閱書籍和上網查找資料,也豐富了自己對的了解。不過本次設計也存在一些不足,暴露了自己對的掌握還有所欠缺。在設計過程中,分頻分的太大,頻率太小的話,頻率太大的話,數碼管顯示

溫馨提示

- 1. 本站所有資源如無特殊說明,都需要本地電腦安裝OFFICE2007和PDF閱讀器。圖紙軟件為CAD,CAXA,PROE,UG,SolidWorks等.壓縮文件請下載最新的WinRAR軟件解壓。

- 2. 本站的文檔不包含任何第三方提供的附件圖紙等,如果需要附件,請聯系上傳者。文件的所有權益歸上傳用戶所有。

- 3. 本站RAR壓縮包中若帶圖紙,網頁內容里面會有圖紙預覽,若沒有圖紙預覽就沒有圖紙。

- 4. 未經權益所有人同意不得將文件中的內容挪作商業或盈利用途。

- 5. 人人文庫網僅提供信息存儲空間,僅對用戶上傳內容的表現方式做保護處理,對用戶上傳分享的文檔內容本身不做任何修改或編輯,并不能對任何下載內容負責。

- 6. 下載文件中如有侵權或不適當內容,請與我們聯系,我們立即糾正。

- 7. 本站不保證下載資源的準確性、安全性和完整性, 同時也不承擔用戶因使用這些下載資源對自己和他人造成任何形式的傷害或損失。

最新文檔

- 袋泡茶企業縣域市場拓展與下沉戰略研究報告

- 中小型型鋼企業縣域市場拓展與下沉戰略研究報告

- 大梁、橫梁、軸箱導軌企業縣域市場拓展與下沉戰略研究報告

- 認證服務企業縣域市場拓展與下沉戰略研究報告

- 制藥系統企業縣域市場拓展與下沉戰略研究報告

- 娛樂、游覽用船舶企業ESG實踐與創新戰略研究報告

- 可塑料企業ESG實踐與創新戰略研究報告

- 電氣音響信號裝置企業縣域市場拓展與下沉戰略研究報告

- 網片定型機企業縣域市場拓展與下沉戰略研究報告

- 2025-2030中國天然肉桂醛行業市場發展趨勢與前景展望戰略研究報告

- 《HSK標準教程3》第1課

- 醫療試劑服務方案

- 《廣州市城市樹木保護專章編制指引》解讀(分享版)

- 醫療設備采購 投標技術方案 (技術方案)

- 星級酒店MOD值班管理規定

- 產品外觀檢驗標準(通用)

- 同濟大學信紙

- 印章封存登記表

- 社會工作者之初級社會工作實務模擬試題及答案A4打印

- 工作交接表excel模板

- 滾筒式柑橘分選機的設計

評論

0/150

提交評論